| 您现在的位置:首页 > 技术资料 |

|

SDH中E1/VC-12异步映射的设计与实现 摘要:分析了同步数字体系中2.048Mlaps支路信号E1异步映射进VC一12 的过程,并根据正/零/负码速调整原理确定了缓冲存储器的容量和正负码速调整的判定门限。通过对异步FIFO读控制实现了此异步映射过程的正/零/负码速调整。同时,为了在异步时钟域之间可靠地传递数据,采用格雷码实现读时钟域对写指针的采样。该设计通过了功能仿真、综合及FPGA验证。 SDH(Synchronous Digital Hierarchy,同步数字体系)是一种有机地接合了高速大容量光纤传输技术和智能网技术的新型传输体制.由于其特有的高度灵活性、可管理性,已经成为光纤通信的一个重要发展方向。2.048Mbps是公用网中基本传输速率,应用极为广泛,将2.048Mbps 支路信号E1(Electfical intefface signal,电接口信号)复用入STM-1(Synchronous Transport Module,同步传送模块)是实现PDH(Plesiochronous Distal Hierarchy,准同步数字系列)与SDH兼容的重要部分。要完成这一工作,需要把2.048Mbps支路信

1 2.048Mbps支路信号E1映射进VC一12复帧的过程 在PDH向SDH过渡的长时期内,2.048Mbps支路信号El需要异步映射入STM一1。由于PDH的一次群支路信号与SDH传输网是非同步的,故2.048Mbps支路信号El必须先装入标准容器C-12中进行适配处理即进行码速调整,使之与SDH网同步。 首先将2.048Mbps支路信号E1经过速率适配装载到对应的标准容器C-12中,为了便于速率的适配采用了复帧的概念,即将4个C-12基帧组成一个复帧。复帧的具体比特安排如图1所示。C-12的基帧频率是8000帧/s.所以C-12复帧的频率也就成了2000帧/s。 为了在SDH网的传输中能实时监测任一个2.048Mbps通道信号的性能,需将C-12再打包,即加入相应的通道开销(低阶通道开销),使其成为VC-12帧结构。 VC-12帧结构如图l所示。V5、J2、N2、K4为VC-12的通道开销字节;8个O比特为开销通信通路比特;49个R比特为固定塞入比特;3个C1 比特为负码速调整控制比特.3个C2比特为正码速调整控制比特,分别用来控制一个负调整机会比特S1和一个正调整机会比特S2。当C1C1C1=000时表示Sl是信息比特,而C1C1C1=111时表示S1是调整比特。C2按同样的方式控制S2比特。S1比特和S2比特作为调整比特时其值未做规定,因而要求接收机将该值忽略。 支路信号El的帧频为8kHz,所以VC-12复帧的频率为2kHz,每复帧中有一个负调整比特Sl和一个正调整比特S2,因此做零调整时净复合速率为: (324×8+O)×2k=2048kbps;做负调整时净复合速率为:(324×8+1)×2k=2050kbps;做正调整时净复合速率为:(324 ×8-1)×2k=2046kbps。 由于E1接口的标称速率及容差为:2048kb/s±50ppm,也就是(2048kb±102.4b)/8,因此(2048kb±2kb)/s完全可以容纳支路信号E1的频偏。所以本设计采用将2.048Mbps支路信号E1通过正/零/负码速调整异步映射入VC-12的设计思路。 2 正/零/负码速调整原理及相关参数的确定 正/零/负码速调整是采用脉冲塞人原理并在支路速率的标称值上进行的。首先为支路缓冲存储器设置两个固定门限:正调整门限Zmin和负调整门限Zmax。由于包装速率fh与支路速率fl都在一定的容差内变化,并且传输时钟各不相同,因此有下列三种情况:读写时差在两门限之间,不做码速调整;读写时差低于正调整门限,要求正调整,即减慢读出时钟(fh),以增大读写时差;读写时差高于负调整门限,要求负调整,即加快读出时钟(fh),以减小读写时差。 读出第x个信码时读写时差△tx的表达式为:

由此可得出稳态码速调整所引起的读写时差峰一峰值: 按照ITU-T G.703建议,异步2.048Mbps网络接口的最大允许输入抖动Jp-p=1.5UI;而且在码速恢复锁相环中,由于输入支路频偏差及压控振荡器中心频率偏移还会引入跟踪误差(峰一峰值变化)。缓冲存储器容量和正调整门限、负调整门限的设定除了要考虑上述因素之外,还要考虑使码速调整过渡过程尽量小,稳定工作区尽量大,并且尽量扩大不调整状态的持续时间,同时又能承受lb的线路抖动。

于是可以得到正调整判决门限为:BT+=Zmin=3Tl 3 异步映射的设计与实现 本设计通过一个异步FIFO对支路信号E1实现正/零/负码速调整。首先对异步FIFO设定两个判决门限值:正调整判决门限值3Tl和负调整判决门限值15Tl。低于或等于正调整判决门限值时值进行正码速调整,高于或等于负调整判决门限值时进行负码速调整,在正负调整判决门限值之间的不进行码速调整。写地址产生模块的时钟由支路信号El提取的时钟信号w_clk(2.098MHz±102. 4CHz)提供,用于产生将E1_data顺序写入双口RAM的写指针;读地址产生模块的时钟由外部时钟信号r_clk(2.240MHz)提供,用于产生双口。RAM的读指针。读写地址比较模块产生读写指针的差值,并与正负调整判决门限值比较,之后将比较结果送给输出控制模块。输出控制模块还受控于帧头信号、帧同步信号。输出控制模块决定是从双口RAM中读取数据VC-12,还是从发送寄存器中读取数据VC-12。整体设计框图如图2所示。

3.1 存储单元的设计 首先定义一个位宽为Ibit、深度为32的双口RAM,用作异步FIFO的存储单元,然后定义写数据端口(data_in)、写时钟(w_elk)、写地址(w_add)、写使能信号(wen)、读数据端口(data_out)、读时钟(r_clk)、读地址(r_add)、读使能信号(ren)等,用以控制此双口RAM的读写操作。 3.2 写指针在写时钟域和读时钟域之间的传递殛读写指针在读时钟域的比较 对此异步映射器而言,它的写是不可控制的,输入的写时钟频率为2.048MHz±102.4Hz。但是读是可控制的,读时钟频率为由外部提供的2.240MHz。因此只需在读时钟域对写指针取样,并把它与读指针进行比较产生正/零/负码速调整信号即可。 由于读写时钟频率不同,为了在写时钟域和读时钟域之间可靠地传递写指针,本设计采用在写时钟域先将写指针的二进制码转换为格雷码,然后用读时钟对此格雷码进行采样;在读时钟域将采样的写指针的格雷码转换为二进制码(wbin_rclk[n:O]),再与读指针的二进制码(rbin_rclk[n:0])进行比较,得到两者之间的差值(ptr_gap[n-l:0])。 为了确定读写指针是否在同一个地址周期。需要对读写指针额外增加一位最高位MSB,用读写指针的最高位判定读写指针是否在同一个地址周期。 在图3中,wbin[n-1:]用于向双口RAM中提供写数据的写指针;由于二进制码和格雷码的最高位相同,因此写指针的二进制码wbin[n:0]的最高位wbin[n]不变,并将除了最高位以外的二进制码转换为格雷码gptr[n-l:0],这样做可以节省一个触发器;wbin[n]和gptr [n1:O]组成wgray_ptr_to_rclk[n:O],用于在读时钟域和写时钟之间传递写指针。

在图4中,wgray_ptr_to_rclk[n:0]为从写时钟域传递到读时钟域的写指针;读写指针比较单元的读指针(rbin_rclk[n:O])来自于读地址产生模块的二进制读指针(rbin__rcLk_in[n:O])。

3.3 输出控制模块 输出控制模块属于读时钟域,根据读时钟r_clk、正/零/负码速调整信号adjust_signal[1:O]以及帧信号(包括帧头信号frame_head和帧同步信号in_frame)等产生输出数据VC-12。输出控制模块的设计框图如图5所示。

输出控制模块由读时钟控制的模8计数器,(n)、模35计数器(m)、模4计数器(p)以及输出选择单元组成,模8计数器的进位用于模35计数,模35计数器的进位用于模4计数。模8计数器用于读出一个字节的8比特。当m=0时从发送寄存器读出8个R、8个R、8个R、8个R;当m=1时从发送寄存器读

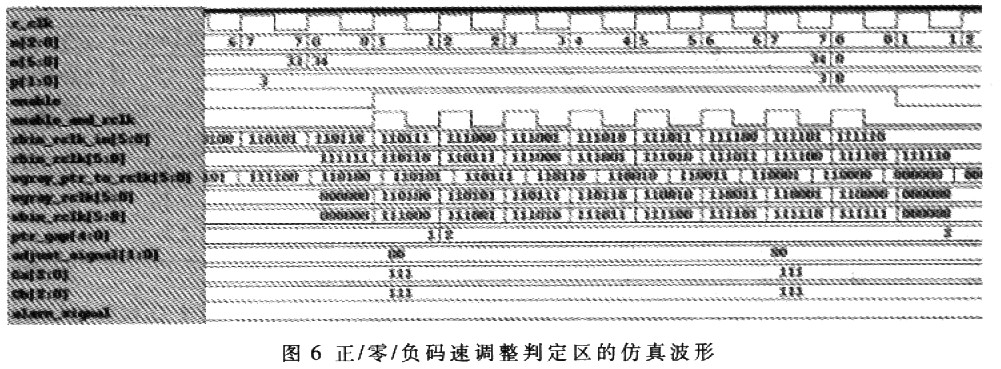

正/零/负码速调整的判定区放于帧末(p=3、m=34时),此时对读写指针进行比较,并根据比较的结果设定正/零/负码速调整信号。然后在下一帧中根据此调整信号进行正/零/负码速调整,并在此帧的判定区设定正/零/负码速调整信号(用于第三帧的码速调整)。同时设定正判决的优先级别高于负判决,即用一帧中的正码速调整判决关闭负码速调整判决。 3.4 功能仿真以爰综合验证 通过可综合的硬件描述语言Verilog实现了此异步映射电路的设计,并且通过了VCS工具的功能仿真。图6给出了正/零/负码速调整判定区的仿真波形图。

图中,enable为进行调整判定的使能信号,r_clk为读时钟信号,rbin_clk_in[5:O]为来自于读地址产生模块的读指针信号, rbin_rclk[5:0]为对rbin_rclk_in[5:O]进行采样后的读指针信号,wgray_ptr_rclk[5:0]为从写时钟域传递到读时钟域的写指针信号,wgray__rclk[5:0]为读时钟对wgray_ptr_to_rctk[5:0]采样后的写指针信号, wbin_rclk[5:0]为二进制码的写指针信号,ptr_gap[4:0]为读写指针的差值信号,adjust_signal[1:0]为正/零/ 负码速调整信号,Ca[2:0]为C1CIC1,Cb[2:0]为C2C2C2,alarm_signal为输入信号性能劣化报警信号。 由此仿真波形图可以看出,由于读写指针的差值ptr_gap[4:0]为2Tl,小于正调整判决门限值3Tl,因此设置负码速调整控制比特C1C1Cl= 111,正码速调整控制比特C2C2C2=111,正/零/负码速调整信号adjust_signal[l:0]=00(这三个值均为二进制码),于是下一帧要进行正码速调整。 实现了功能仿真之后,在Design Compiler综合环境下完成了该系统的综合。最后,采用ALTERA公司的FPGA(Cyclone系列)EPLC6T144C8器件通过了验证。

| |||||||||||||||||

由前面的分析可以得出:若ptr__gap[n-l:0]<4Tl(正调整判决门限为3Tl),则进行正码速调整;若ptr_gap[n-1:0] >14Tl(负调整判决门限为15Tl),则进行负码速调整;若4Tl≤ptr_gap[n-l:0]≤14Tl,则不进行码速调整。 ptr_ gap[n-1:O]的值必须小于32Tl,若大于此值,则说明输入信号E1_data的速率过快或者过慢,超出了(2048k±102.4) bps这个范围,此时产生输入信号性能劣化报警信号,同时发出响应脉冲wren、ren,使对双口RAM的读写操作无效。如果ptr_gap[n-1: 0]<32Tl,则分为以下两种情况:

由前面的分析可以得出:若ptr__gap[n-l:0]<4Tl(正调整判决门限为3Tl),则进行正码速调整;若ptr_gap[n-1:0] >14Tl(负调整判决门限为15Tl),则进行负码速调整;若4Tl≤ptr_gap[n-l:0]≤14Tl,则不进行码速调整。 ptr_ gap[n-1:O]的值必须小于32Tl,若大于此值,则说明输入信号E1_data的速率过快或者过慢,超出了(2048k±102.4) bps这个范围,此时产生输入信号性能劣化报警信号,同时发出响应脉冲wren、ren,使对双口RAM的读写操作无效。如果ptr_gap[n-1: 0]<32Tl,则分为以下两种情况: